## CLS-222 CAMERA LINK SIMULATOR

## **User's Manual**

Document # 201432, Rev 0.3, 05/25/2021

© Vivid Engineering

415 Boston Turnpike #305 • Shrewsbury, MA 01545

Phone 508.842.0165 • Fax 508.842.8930

Email info@vividengineering.com

Web www.vividengineering.com

Camera Link® is a registered trademark of the Automated Imaging Association (AIA)

$Microsoft \ensuremath{\mathbb{R}}$  and  $Windows \ensuremath{\mathbb{R}},$  are registered trademarks of Microsoft Corporation

All other nationally and internationally recognized trademarks and tradenames are hereby acknowledged

# **Table of Contents**

| 1. IN  | ITRODUCTION                            | 1  |

|--------|----------------------------------------|----|

| 1.1.   | Overview                               | 1  |

| 1.2.   | Features                               | 2  |

| 1.3.   | Functional Description                 | 3  |

| 1.3.1. | Timing Generator                       | 5  |

| 1.3.2. | Pattern Generator                      | 7  |

| 1.3.3. | Data Valid (DVAL) Signal               | 16 |

| 1.3.4. | Configuration Memory                   | 17 |

| 1.3.5. | RS-232 Serial Port                     | 18 |

| 1.3.6. | USB Support                            | 18 |

| 1.3.7. | Camera Control Inputs                  | 19 |

| 1.3.8. | Channel Link Transmitters              | 19 |

| 1.3.9. | Power over Camera Link (PoCL) Features | 20 |

| 1.4.   | Command Line Interface (CLI)           | 22 |

| 1.4.1. | Camera Link Mode (CL_MODE)             | 24 |

| 1.4.2. | Continuous Mode (CONTINUOUS)           | 25 |

| 1.4.3. | Exsync Enable (EXSYNC_ENB)             | 26 |

| 1.4.4. | Exsync Select (EXSYNC_SEL)             | 27 |

| 1.4.5. | Linescan Mode (LINESCAN)               | 27 |

| 1.4.6. | Clock Frequency (FREQUENCY)            | 28 |

| 1.4.7. | Line Valid High (LVAL_HI)              | 28 |

| 1.4.8. | Line Valid Low (LVAL_LO)               | 28 |

| 1.4.9. | Frame Valid High (FVAL_HI)             | 29 |

| 1.4.10 | . Frame Valid Low (FVAL_LO)            | 29 |

| 1.4.11 | . Frame Valid Setup (FVAL_SETUP)       | 30 |

| 1.4.12 | . Frame Valid Hold (FVAL_HOLD)         | 30 |

| 1.4.13 | . DVAL Mode (DVAL_MODE)                | 31 |

| 1.4.14 | . DVAL State (DVAL)                    | 31 |

| 1.4.15 | . Clock Disable (CLK_DIS)              | 32 |

| 1.4.16 | . X Dimension Pattern Step (X_STEP)    | 32 |

| 1.4.17 | Y Dimension Pattern Step (Y_STEP)      | 33 |

| 1.4.18 | . Color Bar Width (BAR_WIDTH)          | 33 |

| 1.4.19 | . Bayer Select (BAYER_SEL)             | 34 |

| 1.4.20 |                                        | 34 |

| 1.4.21 |                                        | 34 |

| 1.4.22 | , = ,                                  | 35 |

| 1.4.23 |                                        | 35 |

| 1.4.24 |                                        | 36 |

| 1.4.25.                            | AIA Pattern Select (AIA_SEL)                  | 36           |

|------------------------------------|-----------------------------------------------|--------------|

| 1.4.26. PoCL Mode (POCL_MODE)      |                                               | 37           |

| 1.4.27. PoCL Power Presence (POCL) |                                               | 37           |

| 1.4.28.                            | CC State (CC)                                 | 39           |

| 1.4.29.                            | FPGA Version (VERSION)                        | 39           |

| 1.4.30.                            | One Shot Trigger (ONE_SHOT)                   | 40           |

| 1.4.31.                            | Parameter Save (SAVE)                         | 40           |

| 1.4.32.                            | Parameter Recall (RECALL)                     | 41           |

| 1.4.33.                            | Parameter Dump (DUMP)                         | 42           |

| 1.5. S <sub>1</sub>                | pecifications                                 | 44           |

| 2. IN                              | TERFACE                                       | 45           |

| <b>2.1. F</b> 2.1.1.               | ront Panel Connections Cable Shield Grounding | <b>45</b> 45 |

| 2.2. R                             | tear Panel                                    | 46           |

| 3. ME                              | ECHANICAL                                     | 47           |

| 3.1. D                             | vimensions                                    | 47           |

| 3.2. E                             | xternal Power Supply                          | 48           |

|                                    |                                               |              |

## 1. Introduction

#### 1.1. Overview

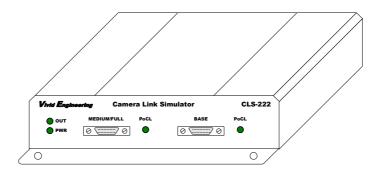

The CLS-222 Camera Link Simulator is an affordable, high-performance video test pattern generator that supports all video formats including those introduced in Camera Link version 2.1. Fully programmable video timing enables the CLS-222 to mimic the characteristics of almost any camera. New features include enhanced timing performance, bayer color support, and additional video patterns. Control is via an RS-232 port, USB, or frame grabber COM port. The CLS-222 also incorporates the AIA validation test pattern.

The CLS-222 incorporates features for testing and exercising Power Over Camera Link (PoCL) interfaces. The CLS-222 detects power and mimics PoCL camera characteristics at both connectors, supporting newer PoCL cameras. Connectors are the smaller SDR/HDR type typically used with PoCL devices

The CLS-222 is very useful for the development and test of Camera Link components and systems, and is easy to use with included quick-configuration software. The CLS-222 is particularly useful for testing PoCL cables and PoCL frame grabber functionality.

#### 1.2. Features

- Supports all Camera Link configurations (base/medium/full/72-bit/80-bit)

- Fully programmable video timing, mimics almost any camera

- Supports all video formats including new Camera Link v2.1

- PoCL power detect at both connectors

- Mimics PoCL camera characteristics

- Video pattern options include wedge, color-bar, and pseudo-random

- Bayer color support

- Area and line scan formats

- "Roll" feature adds pattern motion

- Triggered (exsync) modes

- Supports AIA validation test pattern sequences

- Easy to use with included quick-configuration software. May also be programmed via a command line interface

- Downloadable configuration files are easily created and modified

- Controlled via an RS-232 port, USB (via optional adapter), or frame grabber comm port

- Operates from 10 MHz to 95 MHz, above/below the normal Camera Link 20-85 MHz range for performance/margin testing

- Can operate standalone using stored user configurations

- Sturdy aluminum enclosure w/ mounting flange

- Multi-nation power supply and RS-232 cable included

- Made in USA, 3-year warrantee

## 1.3. Functional Description

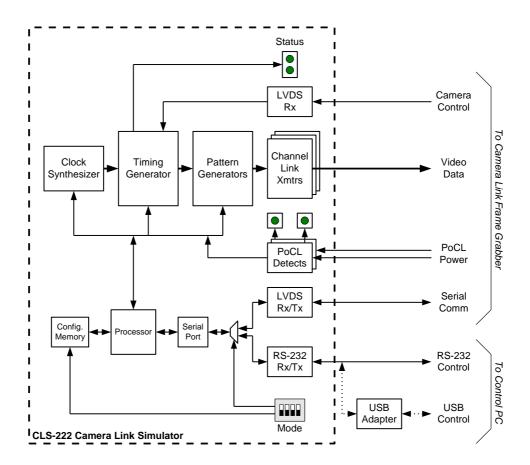

The CLS-222 Camera Link Simulator is a programmable video test pattern generator supporting all Camera Link configurations (base, medium, full, 72-bit, 80-bit). All video formats are supported including Camera Link version 2.1. A block diagram is provided in Figure 1-1.

The clock synthesizer, timing generator, and pattern generator functions combine to generate the desired video test image characteristics.

Control of the CLS-222 is via a simple Command Line Interface (CLI). This enables the CLS-222 to be controlled using any computer incorporating a standard RS-232 serial port, or USB using optional adapter. The CLS-222 may also be controlled from the attached frame grabber via the serial communications port that is part of the Camera Link interface. Users may interactively assign settings via the command line interface, or may download configuration files created in advance. Command file generation is simplified using the included Quick Configurator software.

The CLS-222 incorporates non-volatile memory for storing user configuration settings. Saved settings are automatically loaded upon power-up, enabling operation of the CLS-222 using pre-loaded parameters without a host computer.

The CLS-222 clock synthesizer enables the user to select test pattern pixel clock frequencies between 10 and 95 MHz. Note this is beyond the 20-85 MHz range in the camera Link specification and is provided to support performance/margin testing. The camera control inputs of the Camera Link interface are sent to timing generator for use as exsync inputs, enabling the frame grabber to trigger pattern generation if desired. The serial link in the Camera Link interface, when not being used to control the CLS-222, is looped back to the frame grabber enabling loopback test of the serial interface.

The CLS-222 camera interface incorporates the connector, signals, pinout, and chipset in compliance with the Camera Link version 2.1 specification. The CLS-222 incorporates the "base", "medium", "full", "72-bit", and "80-bit" configuration signal sets, consisting of video data, camera control, and serial communications.

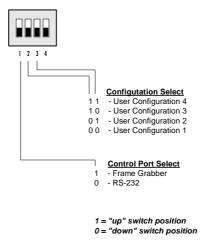

Front panel status LEDs indicate when the unit is powered, and when the CLS-222 is outputting video data. The rear panel incorporates a 4-position mode switch. The mode switch is used to select the controlling interface (RS-232 connector or frame grabber serial port), as well as selecting between up-to 4 user-created configurations.

The CLS-222 is powered by an external multi-nation wall plug-in power supply which is included. Also included is an RS-232 serial cable. An external adapter for controlling the CLS-222 via USB is optional.

Figure 1-1: CLS-222 Block Diagram

## 1.3.1. Timing Generator

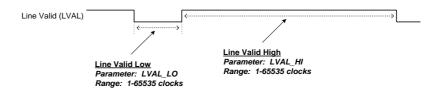

The timing generator establishes the basic video timing characteristics by generating the Line Valid (LVAL) and Frame Valid (FVAL) timing signals. The circuit operates at the selected pixel clock frequency.

LVAL is used to envelope *lines* of video data and is defined in the Camera Link specification as *high* for valid line data. Two CLS-222 timing parameters, LVAL\_LO and LVAL\_HI, determine the duration of LVAL low and high states in pixel clock cycles, respectively. The CLS-222 supports "LVAL low" and "LVAL high" times from 1-65535 pixel clocks. LVAL timing characteristics are shown in Figure 1-2.

Figure 1-2: Line Valid (LVAL) Timing Characteristics

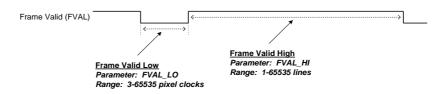

FVAL is used to envelope *frames* of video data from frame scan cameras and is defined in the Camera Link specification as *high* for valid frame data. Two CLS-222 timing parameters, FVAL\_LO and FVAL\_HI, determine the duration of FVAL low and high states in video lines, respectively. Video lines refer to the Line Valid (LVAL) signal discussed in the last paragraph. The CLS-222 supports FVAL low times of 3-65535 pixel clocks and FVAL high times of 1-65535 lines. FVAL timing characteristics are shown in Figure 1-3.

*Note the minimum FVAL\_LO setting is 3.*

Figure 1-3: Frame Valid (FVAL) Timing Characteristics

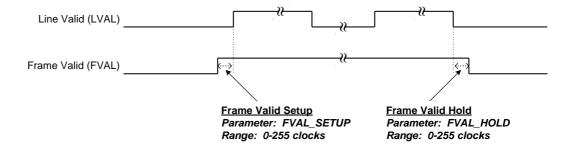

The relative positioning of the FVAL and LVAL timing signals is programmable and is specified using the Frame Valid Setup (FVAL\_SETUP) and Frame Valid Hold (FVAL\_HOLD) parameters.

When FVAL\_SETUP and FVAL\_HOLD are both set to 0, the minimum condition occurs whereby transitions on the FVAL signal occur coincident with the rising edge of the first LVAL in the frame, and the falling edge of the last LVAL in the frame. The FVAL\_SETUP value may be increased to provide "setup" time on the FVAL signal prior to the start of the first line in the frame. Similarly, FVAL\_HOLD may be increased to provide "hold" time on the FVAL signal following the last line in the frame. This relationship is illustrated in Figure 1-4. The figure is a 2-line frame for illustration purposes.

Figure 1-4: FVAL Setup/Hold Timing Parameters

#### **1.3.2.** Pattern Generator

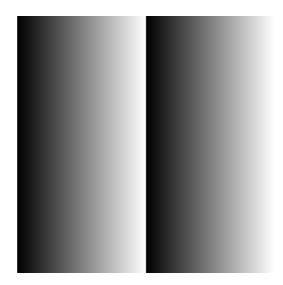

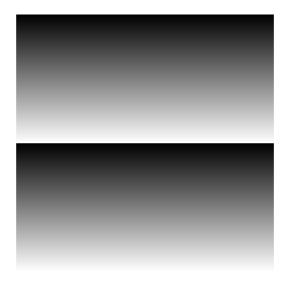

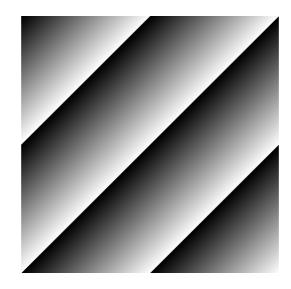

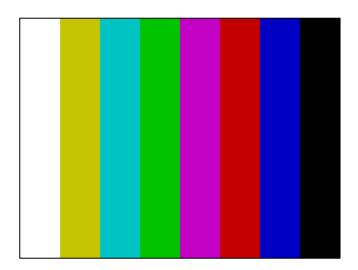

The CLS-222 Camera Link Simulator incorporates a programmable pattern generator to create a variety of test patterns. The CLS-222 is capable of generating fixed-value, horizontal wedge, vertical wedge, diagonal wedge, color bar, pseudo-random, and walking-1 patterns. Example wedge and color bar patterns are shown in Figures 1-5 through 1-8.

Camera Link transmits up-to ten pixels simultaneously (i.e. 8-bit 10-tap mode). The CLS-222 enables the user to select pattern characteristics on a per-pixel basis, denoting the ten pixels A/B/C/D/E/F/G/H/I/J. To support this feature, ten Pattern Select (A\_PATSEL, B\_PATSEL, C\_PATSEL, D\_PATSEL, E\_PATSEL, F\_PATSEL, G\_PATSEL, H\_PATSEL, I\_PATSEL, J\_PATSEL) parameters are provided. The PATSEL parameters are defined in Table 1-1.

**Table 1-1: PATSEL Parameter Definition**

| Pattern Select Value (A_PATSEL, B_PATSEL, C_PATSEL, D_PATSEL (E_PATSEL, F_PATSEL, G_PATSEL, H_PATSEL, I_PATSEL, J_PATSEL) | Video Test Pattern |

|---------------------------------------------------------------------------------------------------------------------------|--------------------|

| 0                                                                                                                         | Fixed Value        |

| 1                                                                                                                         | Horizontal Wedge   |

| 2                                                                                                                         | Vertical Wedge     |

| 3                                                                                                                         | Diagonal Wedge     |

| 4                                                                                                                         | Color Bars         |

| 5                                                                                                                         | Pseudo-Random      |

| 6                                                                                                                         | Walking-1          |

For the fixed value pattern, ten Pixel Fixed Value (A\_FIXED, B\_FIXED, C\_FIXED, D\_FIXED, E\_FIXED, F\_FIXED, G\_FIXED, H\_FIXED, I\_FIXED, J\_FIXED) parameters are provided to individually select static pixel values.

The CLS-222 provides a selectable pixel step size when generating wedge (horizontal, vertical, diagonal) patterns. The step size determines the amount by which pixel values are incremented from pixel-to-pixel and from line-to-line in the test images. Individual "X" (X\_STEP) and "Y" (Y\_STEP) settings are provided. The pixel step size feature is particularly valuable for high-resolution (i.e. 12 or 16-bit) video, and with multi-tap formats.

When generating wedge (horizontal, vertical, diagonal) patterns, the CLS-222 enables the user to select the initial value of each pixel. This is the value associated with the first pixel in the video frame. The value then increments, according to the wedge pattern and X/Y step settings. The pixel initial value feature is particularly valuable in generating wedge patterns while simulating multi-tap cameras. Ten Initial Value (A\_INIT, B\_ INIT, C\_ INIT, D\_ INIT, E\_ INIT, F\_ INIT, G\_ INIT, H\_ INIT, I\_ INIT, J\_ INIT) parameters are provided.

The CLS-222 "roll" feature used in conjunction with the wedge patterns (horizontal, vertical, diagonal) to introduce test pattern motion. When roll is enabled, the starting pixel value in the video test pattern increments every frame. This changes all pixel values within the pattern every frame and adds a "rolling" motion to the displayed pattern. This feature is particularly useful during testing and for debugging image acquisition problems.

The CLS-222 supports all modes defined in the Camera Link v2.1 specification. The configurations consist of "base", "medium", "full", "72-bit" and "80-bit". These modes range from simple 8-bit single-tap, to complex 80-bit color timeslice formats. The desired mode is selected using the Camera Link Mode (CL\_MODE) parameter. The CL\_MODE parameter is defined in Tables 1-2 through 1-6.

Table 1-2: CL\_MODE Parameter Definition, 8-bit Pixels

| CL_MODE Parameter Setting (decimal) | Camera Link Mode<br>(8-bit pixels)        |

|-------------------------------------|-------------------------------------------|

| 0                                   | 1-tap mono (base config)                  |

| 1                                   | 2-tap mono (base config)                  |

| 2                                   | 3-tap mono (base config)                  |

| 3                                   | 4-tap mono (med config)                   |

| 4                                   | 5-tap mono (med config)                   |

| 5                                   | 6-tap mono (med config)                   |

| 6                                   | 7-tap mono (full config)                  |

| 7                                   | 8-tap mono (full config)                  |

| 8                                   | 9-tap mono (72bit config)                 |

| 9                                   | 10-tap mono (80bit config)                |

| 16                                  | 1-tap color RGB (base config)             |

| 17                                  | 2-tap color RGB (med config)              |

| 18                                  | 3-tap color RGB (full config)             |

| 19                                  | 1-tap color RGBI (med config)             |

| 20                                  | 2-tap color RGBI (full config)            |

| 21                                  | 1-tap color Bayer (base config)           |

| 22                                  | 2-tap color Bayer (base config)           |

| 208                                 | 10-tap color RGB timeslice (80bit config) |

Table 1-3: CL\_MODE Parameter Definition, 10-bit Pixels

| CL_MODE Parameter Setting (decimal) | Camera Link Mode<br>(10-bit pixels)       |

|-------------------------------------|-------------------------------------------|

| 32                                  | 1-tap mono (base config)                  |

| 33                                  | 2-tap mono (base config)                  |

| 34                                  | 3-tap mono (med config)                   |

| 35                                  | 4-tap mono (med config)                   |

| 36                                  | 5-tap mono (full config)                  |

| 37                                  | 6-tap mono (full config)                  |

| 38                                  | 7-tap mono (80bit config)                 |

| 39                                  | 8-tap mono (80bit config)                 |

| 48                                  | 1-tap color RGB (med config)              |

| 49                                  | 2-tap color RGB (full config)             |

| 50                                  | 1-tap color RGBI (med config)             |

| 51                                  | 2-tap color RGBI (80bit config)           |

| 52                                  | 1-tap color Bayer (base config)           |

| 53                                  | 2-tap color Bayer (base config)           |

| 209                                 | 10-tap color RGB timeslice (80bit config) |

Table 1-4: CL\_MODE Parameter Definition, 12-bit Pixels

| CL_MODE Parameter Setting (decimal) | Camera Link Mode<br>(12-bit pixels) |

|-------------------------------------|-------------------------------------|

| 64                                  | 1-tap mono (base config)            |

| 65                                  | 2-tap mono (base config)            |

| 66                                  | 3-tap mono (med config)             |

| 67                                  | 4-tap mono (med config)             |

| 68                                  | 5-tap mono (full config)            |

| 69                                  | 6-tap mono (full config)            |

| 80                                  | 1-tap color RGB (med config)        |

| 81                                  | 2-tap color RGB (full config)       |

| 82                                  | 1-tap color RGBI (med config)       |

| 83                                  | 1-tap color Bayer (base config)     |

| 84                                  | 2-tap color Bayer (base config)     |

Table 1-5: CL\_MODE Parameter Definition, 14-bit Pixels

| CL_MODE Parameter Setting (decimal) | Camera Link Mode<br>(14-bit pixels) |

|-------------------------------------|-------------------------------------|

| 96                                  | 1-tap mono (base config)            |

| 97                                  | 2-tap mono (med config)             |

| 98                                  | 3-tap mono (med config)             |

| 99                                  | 4-tap mono (full config)            |

| 100                                 | 5-tap mono (72bit config)           |

| 112                                 | 1-tap color RGB (med config)        |

| 113                                 | 1-tap color RGBI (full config)      |

| 114                                 | 1-tap color Bayer (base config)     |

Table 1-6: CL\_MODE Parameter Definition, 16-bit Pixels

| CL_MODE Parameter Setting (decimal) | Camera Link Mode<br>(16-bit pixels) |

|-------------------------------------|-------------------------------------|

| 128                                 | 1-tap mono (base config)            |

| 129                                 | 2-tap mono (med config)             |

| 130                                 | 3-tap mono (med config)             |

| 131                                 | 4-tap mono (full config)            |

| 132                                 | 5-tap mono (80bit config)           |

| 144                                 | 1-tap color RGB (med config)        |

| 145                                 | 1-tap color RGBI (full config)      |

| 146                                 | 1-tap color Bayer (base config)     |

Figure 1-5: Horizontal Wedge Test Pattern

Figure 1-6: Vertical Wedge Test Pattern

Figure 1-7: Diagonal Wedge Test Pattern

Figure 1-8: Color Bars Test Pattern

## 1.3.3. Data Valid (DVAL) Signal

The CLS-222 includes features to mimic low-speed cameras which utilize the Data Valid (DVAL) signal in the Camera Link interface. Camera Link requires a minimum pixel clock rate of 20 MHz. To support cameras and sensors with pixel rates below 20 MHz, the Camera Link interface provides the Data Valid signal which qualifies the data received from the camera. This capability enables a camera to provide a pixel clock of at least 20 MHz, but qualify only a portion of the data sent, effectively providing a sub 20 MHz pixel clock.

The data valid features are controlled using the DVAL and DVAL\_MODE control registers. When DVAL\_MODE is set to 0, activity on the DVAL signal is disabled and DVAL is held at the static state specified by the DVAL control register. When DVAL\_MODE is set to 1-3, the DVAL signal is active (high) every 2nd, 4th, or 8th clock cycle. Data changes occur coincident with the DVAL signal's high-state. The video test pattern data and timing signals from the CLS-222 are automatically replicated (i.e. stalled) for 2/4/8 clock cycles in order to simulate oversampled data coming from cameras that are utilizing the DVAL signal. This is the typical use of DVAL in order to support low pixel clock frequency cameras in Camera Link systems.

See the DVAL and DVAL control register definitions for more information.

#### 1.3.4. Configuration Memory

The CLS-222 incorporates non-volatile configuration memory for the storage of user-selected parameters. Upon power-up initialization, the CLS-222 automatically recalls the parameter set stored in memory. This feature enables operation of the CLS-222 without a control port connection. The CLI Parameter Save (SAVE) command is used to store the current parameter set to the configuration memory. The CLI Parameter Recall (RECALL) command configures the CLS-222 using the parameter set currently stored.

The CLS-222 holds up to four user configurations. Selection is via the rearpanel mode switch (see Figure 1-9). Note that the mode switch also selects the CLS-222 control port, RS-232 or frame grabber (i.e. serial port in Camera Link interface).

Figure 1-9: Mode Switch Definition

#### 1.3.5. RS-232 Serial Port

The CLS-222 Camera Link Simulator incorporates a standard RS-232 serial port for linking the CLS-222 to a host PC. The serial port provides RS-232 signal characteristics and incorporates a standard 9-pin D-Sub (DB9) connector. The serial port protocol settings are conventional and are defined in Table 1-3. Connector information is provided in Section 2.2.

Table 1-3: RS-232 Serial Port Settings

| Port Characteristic    | Setting |

|------------------------|---------|

| Rate (bits per second) | 9600    |

| Data Bits              | 8       |

| Parity                 | None    |

| Stop Bits              | 1       |

| Flow Control           | None    |

#### 1.3.6. USB Support

Alternatively, the CLS-222 Camera Link Simulator may be connected to the host computer USB port using an optional external USB to serial RS-232 adapter. One side of the USB to serial adapter plugs into the PC USB port. The other side of the adapter connects to the RS-232 serial cable included with the CLS-222. Once installed, the PC will create a new serial COM port that may be accessed using the PC in the same fashion as the standard RS-232 serial port. Driver software is included with the USB adapter.

A USB to serial converter is available from Vivid. These converters are also available from computer supply retailers.

## 1.3.7. Camera Control Inputs

The CLS-222 Camera Link Simulator receives four Camera Control (CC1, CC2, CC3, CC4) from the frame grabber as defined in the Camera Link specification. The camera control signal states can be monitored using the CLI, or used as an exsync input to trigger frame/line output.

CLS-222 can be programmed to select a camera control input (CC1, CC2, CC3, or CC4) for use as an exsync trigger. Exsync trigger polarity (rising or falling edge) is also programmable. When configured, the CLS-222 will issue a single frame (or line in linescan mode) in response to each exsync trigger received.

#### 1.3.8. Channel Link Transmitters

The CLS-222 Camera Link Simulator incorporates Channel Link transmitter devices for outputting video timing, data, and clock in compliance with the Camera Link v2.1 specification. Three Channel Link transmitter devices are used, one for the "base" connector and two for the "medium/full" connector

Channels not in use are disabled. For instance, in 8-bit single tap mode which is a "base" configuration mode, the "medium" and "full" transmitters are disabled

The Camera Link and device specifications define a 20-85 MHz operating range. CLS-222 is tested to verify an extended operating range of 10-95 MHz. This ability to operate above/below the normal Camera Link range is useful for performance and margin testing.

The Channel Link transmitter chips are authentic Texas Instruments DS90CR287MTD devices per the Camera Link specification.

## 1.3.9. Power over Camera Link (PoCL) Features

The Camera Link Specification includes a version of Camera Link in which power is supplied to the camera via the frame grabber over the Cable Link cable(s). This is known as Power over Camera Link, abbreviated PoCL. Details of the PoCL scheme including an explanation of the SafePower feature, which safely energizes PoCL cameras, are provided in the Camera Link specification.

The CLS-222 incorporates the following features for testing and exercising Power over Camera Link (PoCL) interfaces. These features are particularly useful for testing PoCL cables and PoCL frame grabber functionality:

- Smaller SDR/HDR connectors

- 10K ohm resistive sense loads

- Power presence detectors

- PoCL camera emulation

The CLS-222 incorporates the smaller SDR/HDR connector typically used with PoCL cameras. This facilitates testing both the PoCL frame grabber as well as the PoCL cables used to connect the camera to the frame grabber.

The CLS-222's Camera Link interface includes 10K ohm resistive loads at both the *base* and *medium/full* connectors as specified in the Camera Link specification for PoCL. The CLS-222 will appear as a PoCL camera to frame grabbers that support PoCL. The 10K loads are always present. The CLS-222 does not include a provision to "short" the 10K ohm load which would make the CLS-222 appear to be a non-PoCL camera.

The CLS-222 independently detects 12v power presence from the frame grabber at the *base* and *medium/full* connectors. The threshold voltage for power detection is approximately 10v. PoCL power presence is available to the host computer via the CLI (see PoCL command). Power presence is also shown on the front-panel indicators. The simulator consumes approximately 250mW of PoCL power at each connector.

The CLS-222 mimics both PoCL and non-PoCL cameras. For non-PoCL cameras, the CLS-222 video outputs are enabled regardless of PoCL power presence. To mimic PoCL cameras which are powered through the Camera Link cable(s), CLS-222 video outputs are only enabled when PoCL voltage is detected at either the *base* or the base <u>and</u> *medium/full* connectors (see

POCL\_MODE control register). This option enables the CLS-222 to mimic newer PoCL cameras that require power at both connectors. Disabling video output is performed by placing the Texas Instruments DS90CR287MTD transmitter chips in "powder down" mode.

#### 1.4. Command Line Interface (CLI)

The CLS-222 is controlled using a simple Command Line Interface (CLI). The CLI may be accessed via standard terminal emulation software (Tera Term, Putty, Hyperterminal, serial port in MATLAB, etc). There is also a terminal window in the included Quick Configurator software.

Upon power-up, the CLS-222 performs a brief system initialization and will respond with the following message:

```

CLS-222 Camera Link Simulator

Command Line Interface (CLI)

Vivid Engineering

Rev 1.0

```

The CLS-222 recognizes the commands defined in the following sections. In the case of invalid syntax, the CLS-222 responds:

```

invalid

```

Accepted write commands receive the following response:

ok

Sequences of commands are easily created with a text editor (i.e. ".txt" files), saved, and downloaded as desired into the CLS-222. Similarly, current CLS-222 configuration is visible via a DUMP command and can be copied and stored to a file. The included Quick Configurator includes "buttons" for reading and writing configuration files. Spaces, tabs, and returns may be inserted as desired for readability. Comments are indicated using a backslash "/" and may be located at the start of a line or following a command. The following is an example of comments located in a configuration file. Note that numeric information may be entered in either decimal or hexadecimal (0x...) format. An example configuration file is found in Section 1-5.

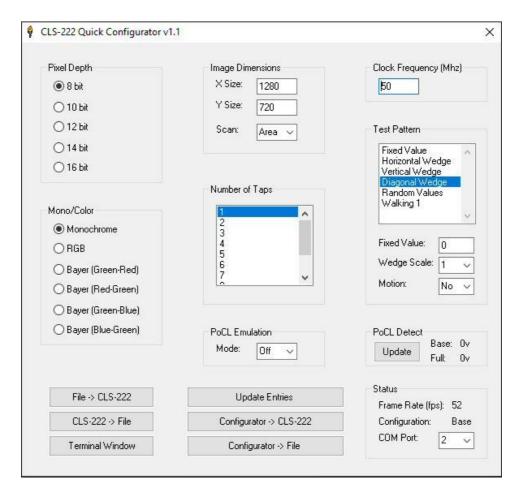

The included Quick Configuration software (Windows XP,7,8,10) is shown in Figure x.x and features an easy-to-use GUI for selecting test image characteristics. The GUI automatically generates the corresponding CLI command set. The command set may be sent to a file, or directly to the CLS-222

device. The Quick Configurator is very useful for "getting started" quickly. Configuration files created using Quick Configurator are easily edited to "fine tune" the CLS-222 commands as needed.

Figure 2-1: Quick Configurator GUI

#### 1.4.1. Camera Link Mode (CL\_MODE)

Parameter:

Settings:

The Camera Link Mode (CL\_MODE) command determines the test pattern pixel format. The CLS-222 generates video test patterns for all Camera Link modes per the v2.1 specification (i.e. base,medium,full,72-bit,80-bit configurations). Note that "taps" refers to the number of pixels sent at a time. See Section 1.3.2 for further information.

CL\_MODE 0 = 8-bit 1-tap mono (base config) 1 = 8-bit 2-tap mono (base config) 2 = 8-bit 3-tap mono (base config) 3 = 8-bit 4-tap mono (med config) 4 = 8-bit 5-tap mono (med config) 5 = 8-bit 6-tap mono (med config) 6 = 8-bit 7-tap mono (full config) 7 = 8-bit 8-tap mono (full config) 8 = 8-bit 9-tap mono (72bit config) 9 = 8-bit 10-tap mono (80bit config) = 8-bit 1-tap color RGB (base config) 16 17 = 8-bit 2-tap color RGB (med config) 18 = 8-bit 3-tap color RGB (full config) 19 = 8-bit 1-tap color RGBI (med config) 20 = 8-bit 2-tap color RGBI (full config) 21 = 8-bit 1-tap color Bayer (base config) = 8-bit 2-tap color Bayer (base config) 22 208 = 8-bit 10-tap color RGB timeslice (80bit config) 32 = 10-bit 1-tap mono (base config) 33 = 10-bit 2-tap mono (base config) 34 = 10-bit 3-tap mono (med config) 35 = 10-bit 4-tap mono (med config) 36 = 10-bit 5-tap mono (full config) 37 = 10-bit 6-tap mono (full config) 38 = 10-bit 7-tap mono (80bit config) 39 = 10-bit 8-tap mono (80bit config) 48 = 10-bit 1-tap color RGB (med config) 49 = 10-bit 2-tap color RGB (full config) 50 = 10-bit 1-tap color RGBI (med config) 51 = 10-bit 2-tap color RGBI (80bit config) 52 = 10-bit 1-tap color Bayer (base config) = 10-bit 2-tap color Bayer (base config) 53

```

209

= 10-bit 10-tap color RGB timeslice (80bit config)

64

= 12-bit 1-tap mono (base config)

65

= 12-bit 2-tap mono (base config)

66

= 12-bit 3-tap mono (med config)

= 12-bit 4-tap mono (med config)

67

68

= 12-bit 5-tap mono (full config)

69

= 12-bit 6-tap mono (full config)

80

= 12-bit 1-tap color RGB (med config)

81

= 12-bit 2-tap color RGB (full config)

82

= 12-bit 1-tap color RGBI (med config)

83

= 12-bit 1-tap color Bayer (base config)

84

= 12-bit 2-tap color Bayer (base config)

96

= 14-bit 1-tap mono (base config)

97

= 14-bit 2-tap mono (med config)

98

= 14-bit 3-tap mono (med config)

99

= 14-bit 4-tap mono (full config)

100 = 14-bit 5-tap mono (72bit config)

112

= 14-bit 1-tap color RGB (med config)

113 = 14-bit 1-tap color RGBI (full config)

114 = 14-bit 1-tap color Bayer (base config)

128

= 16-bit 1-tap mono (base config)

129

= 16-bit 2-tap mono (med config)

130 = 16-bit 3-tap mono (med config)

131 = 16-bit 4-tap mono (full config)

132 = 16-bit 5-tap mono (80bit config)

144 = 16-bit 1-tap color RGB (med config)

145

= 16-bit 1-tap color RGBI (full config)

146 = 16-bit 1-tap color Bayer (base config)

```

Type: Read/Write

Write Example: CL\_MODE 0

Read Example: CL\_MODE ?

#### 1.4.2. Continuous Mode (CONTINUOUS)

The Continuous Mode (CONTINUOUS) command enables continuous output of video test patterns. When continuous mode is enabled, the CLS-222 outputs continuous video data. When disabled, video pattern data is suspended, awaiting an exsync pulse, software one-shot command, or return to continuous mode.

Parameter: CONTINUOUS

Settings: 0 (0x0) = Continuous Mode Disabled

1 (0x1) = Continuous Mode Enabled

Type: Read/Write

Write Example: CONTINUOUS 1 Read Example: CONTINUOUS ?

## 1.4.3. Exsync Enable (EXSYNC\_ENB)

The Exsync Enable (EXSYNC\_ENB) command enables triggered output of pattern frames (or lines in LINESCAN mode) using the camera control inputs (CC1, CC2, CC3, CC4). The exsync camera control input source and active edge are selected using the EXSYNC\_SEL command.

Parameter: EXSYNC\_ENB

Settings: 0 (0x0) = Exsync Triggering Disabled

1(0x1) = Exsync Triggering Enabled

Type: Read/Write

Write Example: EXSYNC\_ENB 0

Read Example: EXSYNC\_ENB ?

## 1.4.4. Exsync Select (EXSYNC\_SEL)

The Exsync Select (EXSYNC\_SEL) command select which camera control input and active edge is used when generating exsync-triggered video patterns. The CLS-222 supports exsync triggered frame generation using any of Camera Link camera control inputs. The triggering edge is selectable as "rising" (low-to-high transition) or "falling" (high-to-low transition).

Parameter: EXSYNC\_SEL

Settings: 0 (0x0) = CC1 rising edge

1 (0x1) = CC1 falling edge 2 (0x2) = CC2 rising edge 3 (0x3) = CC2 falling edge 4 (0x4) = CC3 rising edge 5 (0x5) = CC3 falling edge 6 (0x6) = CC4 rising edge 7 (0x7) = CC4 falling edge

Type: Read/Write

Write Example: EXSYNC\_SEL 0

Read Example: EXSYNC\_SEL?

## 1.4.5. Linescan Mode (LINESCAN)

The Linescan Mode (LINESCAN) command places the CLS-222 in linescan mode. When linescan mode is disabled, the CLS-222 defaults to framescan mode.

Parameter: LINESCAN

Settings: 0 (0x0) = Framescan Mode

1 (0x1) = Linescan Mode

Type: Read/Write

Write Example: LINESCAN 0 Read Example: LINESCAN?

## 1.4.6. Clock Frequency (FREQUENCY)

The Clock Frequency (FREQUENCY) command enables the user to select the Camera Link reference clock in the 10-95 MHz range. Note this range is beyond the 20-85 MHz range defined in the Camera Link specification and is useful for margin and performance testing purposes.

Parameter: FREQUENCY

Range: 10-95 MHz

Type: Read/Write

Write Example: FREQUENCY 50 Read Example: FREQUENCY ?

## 1.4.7. Line Valid High (LVAL\_HI)

The Line Valid High (LVAL\_HI) command is used to establish the duration, in clock cycles for the "high" (logic 1) portion of the Camera Link Line Valid timing signal. See Section 1.3.1 for further information.

Parameter: LVAL\_HI

Range: 1-65535 clocks

Type: Read/Write

Write Example: LVAL\_HI 1280 Read Example: LVAL\_HI ?

#### 1.4.8. Line Valid Low (LVAL\_LO)

The Line Valid Low (LVAL\_LO) command is used to establish the duration, in clock cycles for the "low" (logic 0) portion of the Camera Link Line Valid timing signal. See Section 1.3.1 for further information.

Parameter: LVAL\_LO

Range: 1-65535 clocks

Type: Read/Write

Write Example: LVAL\_LO 32 Read Example: LVAL\_LO ?

## 1.4.9. Frame Valid High (FVAL\_HI)

The Frame Valid High (FVAL\_HI) command is used to establish the duration, in lines for the "high" (logic 1) portion of the Camera Link Frame Valid timing signal. See Section 1.3.1 for further information.

Parameter: FVAL\_HI

Range: 1-65535 lines

Type: Read/Write

Write Example: FVAL\_HI 720 Read Example: FVAL\_HI ?

#### 1.4.10. Frame Valid Low (FVAL\_LO)

The Frame Valid Low (FVAL\_LO) command is used to establish the duration, in clock cycles for the "low" (logic 0) portion of the Camera Link Frame Valid timing signal. **Note the minimum value of 3**. See Section 1.3.1 for further information.

Parameter: FVAL\_LO Range: 3-65535 clocks Type: Read/Write

Write Example: FVAL\_LO 16

Read Example: FVAL\_LO ?

#### **1.4.11.** Frame Valid Setup (FVAL\_SETUP)

The Frame Valid Setup (FVAL\_SETUP) command determines the number of clock cycles that the rising edge of the Camera Link FVAL signal occurs in advance of the rising edge of the LVAL signal for the first line in a frame. When FVAL\_SETUP is set to 0, the rising edge of FVAL is coincident with the rising edge of LVAL. See Section 1.3.1 for further information.

Parameter: FVAL\_SETUP Range: 0-255 clocks Type: Read/Write

Write Example: FVAL\_SETUP 8

Read Example: FVAL\_SETUP ?

#### 1.4.12. Frame Valid Hold (FVAL\_HOLD)

The Frame Valid Hold (FVAL\_HOLD) command determines the number of clock cycles that the falling edge of the Camera Link FVAL signal occurs following the falling edge of the LVAL signal for the final line in a frame. When FVAL\_HOLD is set to 0, the falling edge of FVAL is coincident with the falling edge of LVAL. See Section 1.3.1 for further information.

Parameter: FVAL\_HOLD

Range: 0-255 clocks

Type: Read/Write

Write Example: **FVAL\_HOLD 8**Read Example: **FVAL\_HOLD ?**

## 1.4.13. DVAL Mode (DVAL\_MODE)

The DVAL Mode (DVAL\_MODE) command determines the timing characteristics of the Camera Link Data Valid output signal. Settings 1-3 enable the CLS-222 to simulate oversampled (2x,4x,8x) video data which is generally used to support low pixel clock frequency cameras in Camera Link systems. See Section 1.3.3 for further information.

Parameter: DVAL\_MODE

Settings: 0 (0x0) = DVAL is a static output per the DVAL

command

1 (0x1) = DVAL asserted (1) every 2nd pixel clock 2 (0x2) = DVAL asserted (1) every 4th pixel clock 3 (0x3) = DVAL asserted (1) every 8th pixel clock

Type: Read/Write

Write Example: **DVAL\_MODE 0**Read Example: **DVAL\_MODE ?**

## 1.4.14. DVAL State (DVAL)

The DVAL State (DVAL) command determines the static state of the Camera Link Data Valid output signal when DVAL\_MODE is set to 0. See Section 1.3.3 for further information.

Parameter: DVAL

Settings: 0 (0x0) = DVAL output set to 0

1(0x1) = DVAL output set to 1

Type: Read/Write

Write Example: **DVAL 1** Read Example: **DVAL ?**

## 1.4.15. Clock Disable (CLK\_DIS)

The Clock Disable (CLK\_DIS) command provides individual disable control for the clock output signals generated by the Channel Link transmitter chips (i.e. base, medium, full) in the Camera Link interface. When disabled, <u>all</u> associated Camera Link interface signals (i.e. clock + data) are inactive.

Parameter: CLK\_DIS

Bit positions: bit 0 = Base transmitter clock output disabled when "1"

bit 1 = Medium transmitter clock output disabled when

"1"

bit 2 = Full transmitter clock output disabled when "1"

bit 3-7 = 0

Type: Read/Write

Write Example: CLK\_DIS 0

Read Example: CLK\_DIS ?

## 1.4.16. X Dimension Pattern Step (X\_STEP)

The "X" Dimension Pattern Step (X\_STEP) command determines the amount by which the pixel value increments for the horizontal and diagonal wedge test patterns from pixel-to-pixel across a line (i.e. as column increments). This feature is particularly useful for multi-tap images and for larger pixel depths (i.e. 14-bit and 16-bit) where settings greater than 1 are desirable. The step is applied to all pixels generated (i.e. A-J). See Section 1.3.3 for further information.

Parameter: X\_STEP

Range: 1 - 255

Type: Read/Write

Write Example: X\_STEP 1

Read Example: X STEP ?

## **1.4.17.** Y Dimension Pattern Step (Y\_STEP)

The "Y" Dimension Pattern Step (Y\_STEP) command determines the amount by which the first pixel value of a line increments in the vertical and diagonal wedge test patterns from line-to-line (i.e. as lines increments). This feature is particularly useful for multi-tap images and for larger pixel depths (i.e. 14-bit and 16-bit) where settings greater than 1 are desirable. The step is applied to all pixels generated (i.e. A-J). See Section 1.3.2 for further information.

Parameter: Y\_STEP

Range: 1 - 255

Type: Read/Write

Write Example: Y\_STEP 1

Read Example: Y\_STEP ?

## 1.4.18. Color Bar Width (BAR\_WIDTH)

The Color Bar Width (BAR\_WIDTH) command determines the width in pixels of each of the eight bars that make up a color bar pattern. For instance, a single-tap RGB 1280x720 image would display one complete color bar pattern when BAR\_WIDTH is set to 160 (i.e. 160x8 = 1280).

Parameter: BAR\_WIDTH

Range: 1 - 255 Type: Read/Write

Write Example: BAR\_WIDTH 160

Read Example: BAR\_WIDTH ?

## 1.4.19. Bayer Select (BAYER\_SEL)

The CLS-222 supports BAYER color encoding which is a type of Color Filter Array (CFA) used in many color cameras. Bayer array consists of alternating rows of red-green and green-blue filters. When CL\_MODE is set to one of the Bayer color modes, BAYER\_SEL determines the colors output in the first two pixels of the image as defined below.

Parameter: BAYER\_SEL Settings: 0 = Green - Red

> 1 = Red - Green 2 = Green - Blue 3 = Blue - Green

Type: Read/Write

Write Example: BAYER\_SEL 0

Read Example: BAYER\_SEL ?

## 1.4.20. Pattern Roll (ROLL)

The Pattern Roll (ROLL) command adds motion to video test patterns. Roll is used in conjunction with the horizontal, diagonal, or vertical wedge patterns. When ROLL is enabled, the starting pixel value is incremented every frame. This changes all pixel values each frame and adds a "rolling" affect to the video test pattern. When disabled, the wedge test patterns are static (no change from frame to frame). See Section 1.3.2 for further information.

Parameter: ROLL

Settings: 0 = Roll disable

1 = Roll enabled

Type: Read/Write

Write Example: ROLL 0

Read Example: ROLL ?

#### 1.4.21. Pixel "A-J" Pattern Select (x\_PATSEL)

Up-to ten pixels (A,B,C,D,E,F,G,H,I,J) are simultaneously output from the CLS-222 depending on CL\_MODE setting. Each pixel pattern is user selectable via ten Pattern Select commands (A-J). See Section 1.3.2 for further information.

Parameters: A\_PATSEL, B PATSEL, ... J\_PATSEL

Range: 0 = Fixed Value

1 = Horizontal Wedge 2 = Vertical Wedge 3 = Diagonal Wedge 4 = Color Bars 5 = Pseudo-Random 6 = Walking-1

Read/Write

Type:

Write Example: A\_PATSEL 3

Read Example: A\_PATSEL ?

## 1.4.22. Pixel "A-J" Fixed Value (x\_FIXED)

Up-to ten pixels (A,B,C,D,E,F,G,H,I,J) are simultaneously output from the CLS-222 depending on CL\_MODE setting. The pattern placed on each pixel is individually selectable via the A-J PATSEL commands. When a PATSEL is set to "fixed", the fixed value found in the corresponding FIXED register is output. See Section 1.3.2 for further information.

Parameter: A FIXED, B FIXED... J FIXED

Range: Depends on pixel depth (i.e. CL\_MODE). 0-65535 max.

Type: Read/Write

Write Example: A\_FIXED 0

Read Example: A\_FIXED ?

## 1.4.23. Pixel "A-J" Init Value (x\_INIT)

Up-to ten pixels (A,B,C,D,E,F,G,H,I,J) are simultaneously output from the CLS-222 depending on CL\_MODE. The A-J INIT commands determine the wedge pattern starting values on a per-pixel basis. This feature is particularly useful for generating wedge patterns with multi-tap formats. See Section 1.3.2 for further information.

Parameter: A\_INIT, B INIT... J INIT

Range: Depends on pixel depth (i.e. CL\_MODE). 0-65535 max.

Type: Read/Write

Write Example: A\_INIT 0

Read Example: A\_INIT ?

#### 1.4.24. AIA Test Enable (AIA TEST)

The AIA Test Pattern (AIA\_TEST) command enables the 410-frame LFSR test patterns proposed at the Camera Link Committee for FPGA validation purposes. Four test patterns exist, one for each camera Link configuration (80-bit, base, medium, full). Pattern selection is made using the AIA\_SEL command described below. When enabled, the CLS-222 will output the 410-frame pattern in continuous, triggered, or one fashion and at the user selected pixel clock frequency as determined by the following control registers:

FREQUENCY

CONTINUOUS

EXSYNC\_ENB

EXSYNC\_SEL

ONE\_SHOT

AIA\_SEL

CLK DIS

A "freeze" mode is also provided in which *only* the 1<sup>st</sup> frame of the 410-frame pattern is output. This single-frame pattern is much easier to acquire and is useful for general functional and performance testing.

Note that the settings in all other control registers are ignored when  $AIA\_TEST = 1$  or 3.

Parameter: AIA\_TEST

Settings: 0(0x0) = AIA test pattern disabled

1 (0x1) = AIA test pattern enabled (410-frame sequence) 3 (0x3) = AIA test pattern enabled (freeze mode, frame 1 of

sequence only)

Type: Read/Write

Write Example: AIA\_TEST 0

Read Example: AIA\_TEST ?

#### 1.4.25. AIA Pattern Select (AIA SEL)

The AIA Pattern Select (AIA\_SEL) command selects which Camera Link configuration (base, medium, full, 80-bit) test pattern is issued when the AIA

LFSR validation pattern is being generated (i.e. AIA\_TEST = 1). Test patterns for base, medium, and full configurations have been added to the original 80-bit pattern at the request of the Camera Link Committee.

Parameter: AIA SEL

Settings: 0 (0x0) = 80-bit LFSR pattern

1 (0x1) = Base configuration LFSR pattern 2 (0x2) = Medium configuration LFSR pattern3 (0x3) = Full configuration LFSR pattern

Type: Read/Write

Write Example: AIA\_SEL 0 Read Example: AIA\_SEL ?

## 1.4.26. PoCL Mode (POCL\_MODE)

The PoCL Mode (POCL\_MODE) command controls the simulator PoCL camera emulation feature. This feature is used to mimic PoCL camera characteristics (i.e. no output from camera unless PoCL power present). When enabled, simulator video output occurs only when PoCL power is present at the *base* connector or at *both* connectors as defined below..

Parameter: PoCL\_Mode

Settings: 0(0x0) = PoCL camera emulation disabled

1 (0x1) = PoCL power required at *base* connector 2 (0x2) = PoCL power required at *both* connectors

Type: Read/Write

Write Example: **POCL\_MODE 0**Read Example: **POCL\_MODE ?**

## 1.4.27. PoCL Power Presence (POCL)

The PoCL Power Presence (POCL) command detects power presence at the Camera Link interface from a PoCL frame grabber. Power is independently detected at both the base and medium/full connectors. This register is read only. See Section x.x.x for further information.

Parameter: **POCL**

0(0x0) = No PoCL power presentSettings:

1(0x1) = PoCL power present at *base* connector 2(0x2) = PoCL power present at *full* connector

3(0x3) = PoCL power present at *both* connectors

Type: Read

Read Example: POCL?

## 1.4.28. CC State (CC)

The CC State (CC) command is used to read the current state of the Camera Link camera control inputs (CC1,CC2,CC3,CC4). This register is read only. See Section 1.3.7 for further information.

Parameter: CC

Bit positions: bit 0 = CC1 (lsb)

bit 1 = CC2bit 2 = CC3bit 3 = CC4bit 4-7 = 0

Type: Read

Read Example: CC?

## 1.4.29. FPGA Version (VERSION)

The FPGA Version (VERSION) command is used to read the hardware version code for the CLS-222 Field Programmable Gate Array (FPGA) device. The standard version code is 17. Note that the firmware version is displayed in the startup messages.

Parameter: VERSION

Settings: 8-bit FPGA version code (17 standard)

Type: Read

Read Example: **VERSION**?

## 1.4.30. One Shot Trigger (ONE\_SHOT)

The One Shot Trigger (ONE\_SHOT) command enables the triggering of a single frame (or line for linescan mode) via the CLI. Note that continuous mode must be disabled to use this feature (see CONTINUOUS command). There is no read or write data associated with this command.

Parameter: ONE\_SHOT

Settings: None, command only

Type: Command

Example: **ONE\_SHOT**

## 1.4.31. Parameter Save (SAVE)

The Parameter Save (SAVE) command stores the current CLS-222 parameter set to non-volatile memory. Up-to four user configurations can be stored. Selection is via the rear panel mode switch. The saved parameters are recalled automatically following power-up, or in response to the RECALL command. Saved parameters are maintained until altered via a subsequent SAVE command. There is no read or write data associated with this command.

Parameter: SAVE

Settings: None, command only

Type: Command

Example: SAVE

## 1.4.32. Parameter Recall (RECALL)

The Parameter Recall (RECALL) command retrieves parameter sets currently stored in non-volatile memory. Up-to four user configurations can be stored and recalled. Selection is via the rear panel mode switch. The saved parameters are also automatically recalled during power-up initialization. There is no read or write data associated with this command.

Parameter: RECALL

Settings: None, command only

Type: Command

Example: **RECALL**

## 1.4.33. Parameter Dump (DUMP)

The Parameter Dump (DUMP) command causes the CLS-222 to return the entire current parameter set to the host computer. Information is displayed in both hexadecimal and decimal format. The dump data can be pasted into a file and used for subsequent download into the CLS-222. Note that the last two entries are read-only and should not be omitted from the file. A typical DUMP command response is shown below.

Parameter: DUMP

Settings: None, command only

Type: Command

Example: **DUMP**

## CLS-222 Dump Example:

| CL MODE    | 0x00   | / | 0    |

|------------|--------|---|------|

| CONTINUOUS | 0x01   | / | 1    |

| EXSYNC ENB | 0x00   | / | 0    |

| EXSYNC_SEL | 0x00   | / | 0    |

| LINESCAN   | 0x00   | / | 0    |

| FREQUENCY  | 0x32   | / | 50   |

| LVAL_HI    | 0x0500 | / | 1280 |

| LVAL_LO    | 0x0020 | / | 32   |

| FVAL_HI    | 0x02D0 | / | 720  |

| FVAL_LO    | 0x0010 | / | 16   |

| FVAL_SETUP | 0x08   | / | 8    |

| FVAL_HOLD  | 0x08   | / | 8    |

| DVAL_MODE  | 0x00   | / | 0    |

| DVAL       | 0x01   | / | 1    |

| CLK_DIS    | 0x0    | / | 0    |

| X_STEP     | 0x01   | / | 1    |

| Y_STEP     | 0x01   | / | 1    |

| BAR_WIDTH  | 0xA0   | / | 160  |

| BAYER_SEL  |        | / | 0    |

| ROLL       | 0x00   | / | 0    |

| A_PATSEL   |        | / | 3    |

| B_PATSEL   | 0x00   | / |      |

| C_PATSEL   | 0x0    | / | 0    |

| D_PATSEL   | 0x00   | / | 0    |

| E_PATSEL   | 0x00   | / | 0    |

| F_PATSEL   | 0x00   | / | 0    |

| G PATSEL   | 0x0    | / | 0    |

| H_PATSEL  | 0x00   | / 0  |

|-----------|--------|------|

| I PATSEL  | 0x00   | / 0  |

| J PATSEL  | 0x0    | / 0  |

| A FIXED   | 0x0000 | / 0  |

| B FIXED   | 0x0000 | / 0  |

| C_FIXED   | 0x0000 | / 0  |

| D_FIXED   | 0x0000 | / 0  |

| E_FIXED   | 0x0000 | / 0  |

| F_FIXED   | 0x0000 | / 0  |

| G FIXED   | 0x0000 | / 0  |

| H_FIXED   | 0x0000 | / 0  |

| I_FIXED   | 0x00   | / 0  |

| J_FIXED   | 0x0    | / 0  |

| A_INIT    | 0x0000 | / 0  |

| B_INIT    | 0x0000 | / 0  |

| C_INIT    | 0x0000 | / 0  |

| D_INIT    | 0x0000 | / 0  |

| E_INIT    | 0x0000 | / 0  |

| FINIT     | 0x0000 | / 0  |

| G_INIT    | 0x0000 | / 0  |

| H_INIT    | 0x0000 | / 0  |

| I_INIT    | 0x0    | / 0  |

| J_INIT    | 0x0    | / 0  |

| AIA TEST  | 0x00   | / 0  |

| AIA SEL   | 0x00   | / 0  |

| POCL MODE | 0x00   | / 0  |

| POCL      | 0x00   | / 0  |

| CC        | 0x0F   | / 15 |

| VERSION   | 0x11   | / 17 |

|           |        |      |

## 1.5. Specifications

Table 1-4: CLS-222 Specifications

| Feature                | Specification                                          |  |

|------------------------|--------------------------------------------------------|--|

| Video Interface        | Camera Link v2.1 base/medium/full/72-bit/80-bit + PoCL |  |

| Video Connectors       | 26-pin SDR/HDR type                                    |  |

| Frequency Range        | 10-95 MHz                                              |  |

| Output Device          | Texas Instruments DS90CR287 (per specification)        |  |

| Serial Port            | RS-232 male 9-pin D-Sub, modem cable included          |  |

| Mode Switch            | 4 position, Control and configuration select           |  |

| Quick-Configuration SW | Windows XP, 7, 8, 10                                   |  |

| Power Supply           | Universal wall style w/ outlet plug set                |  |

| Power Jack             | 2.1 x 5.5 mm, center-positive. Locking style optional  |  |

| Power Requirements     | 5 VDC, 700 mA typical                                  |  |

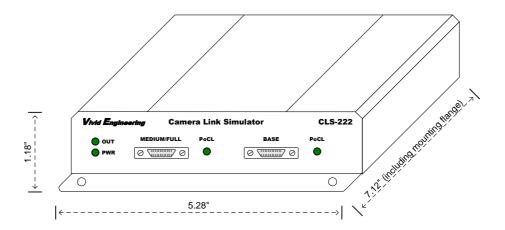

| Cabinet Dimensions     | 5.28" (L) x 1.18" (H) 7.12" (D)                        |  |

| Weight                 | 16 oz                                                  |  |

| Operating Temp Range   | 0 to 50° C                                             |  |

| Storage Temp Range     | -25 to 75° C                                           |  |

| Relative Humidity      | 0 to 90%, non-condensing                               |  |

## 2. Interface

#### 2.1. Front Panel Connections

The CLS-222 Camera Link Simulator front panel is shown in Figure 2-1. The front panel contains two 26-pin SDR/HDR (i.e. miniCL) connectors for connecting to the frame grabber. Camera Link "medium", "full", "72-bit", and "80-bit" configurations utilize both video connectors. "Base" configurations utilize only the "base" connector. The video connector and signal assignment complies with the Camera Link specification.

The "PWR" LED indicates the unit is on. The "OUT" LED indicates the unit is outputting video data.

The two PoCL LEDs, when illuminated, identify PoCL power presence at the respective connector.

Note that the connector pin assignments are as defined for the <u>camera interface</u> in the Camera Link Specification.

Figure 2-1: CLS-222 Front Panel

## 2.1.1. Cable Shield Grounding

Camera Link cable "outer" shields are connected to the CLS-222 aluminum case. The case is isolated from the CLS-222 circuitry and the cable "inner" shields.

The frame grabber cable "inner" shield connects to circuit digital ground, maintaining signal reference levels between the CLS-222 and the frame grabber.

## 2.2. Rear Panel

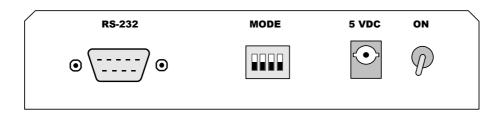

The CLS-222 Camera Link Simulator rear panel is shown in Figure 2-2. The rear panel contains an RS-232 connector, 4-position mode switch, on-off switch, and DC power jack.

The DC power jack accepts either a standard 2.1 x 5.5 mm barrel-style power plug or a special locking plug. The locking plug has bayonet-style "ears" on the barrel. Once inserted, the plug is turned ¼ turn clockwise. This locks the connection and provides retention. Plug polarity is center-positive. Recommended locking power plug is Philmore part number 2150 or Shogyo MP-121AR.

The RS-232 serial port connector is a standard 9-pin male D-Sub type (DB9). Connection to PC, USB adapter, etc is via a null-modem cable (included).

Figure 2-2: CLS-222 Rear Panel

## 3. Mechanical

## 3.1. Dimensions

The CLS-222 Camera Link Simulator cabinet dimensions are shown in Figure 3-1.

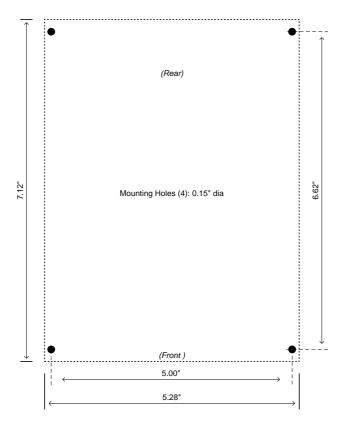

The CLS-222 is housed in a sturdy aluminum enclosure. The body is extruded aluminum, with detachable front and rear endplates. The enclosure incorporates a mounting flange. The flange contains four predrilled holes (0.15" diameter) for convenient equipment mounting. A mounting drawing is provided in Figure 3-2.

Figure 3-1: CLS-222 Cabinet Dimensions

Figure 3-2: Mounting Holes

## 3.2. External Power Supply

The CLS-222 is powered by 5 VDC and incorporates a 2.1 x 5.5 mm DC power jack that accepts either a standard barrel-style power plug, or a special locking version. Power plug polarity is center-positive.

The CLS-222 includes a multi-nation wall-mount power supply that handles a wide power range (90-264 VAC, 47-63 Hz) and comes with a set of outlet plugs suitable for most countries (US, Europe, UK, etc). The CLS-222 may also be purchased with a locking-plug power supply, or without power supply.

# 4. Revision History

Table 4-1: CLS-222 User's Manual Revision History

| Document ID# | Date      | Changes                       |

|--------------|-----------|-------------------------------|

| 201432-0.1   | 9/23/2019 | Preliminary release of manual |

| 201432-0.2   | 7/28/2020 | Corrects Table 1-6            |

| 201432-0.3   | 5/25/2021 | Corrects Section 1.4.1        |

|              |           |                               |